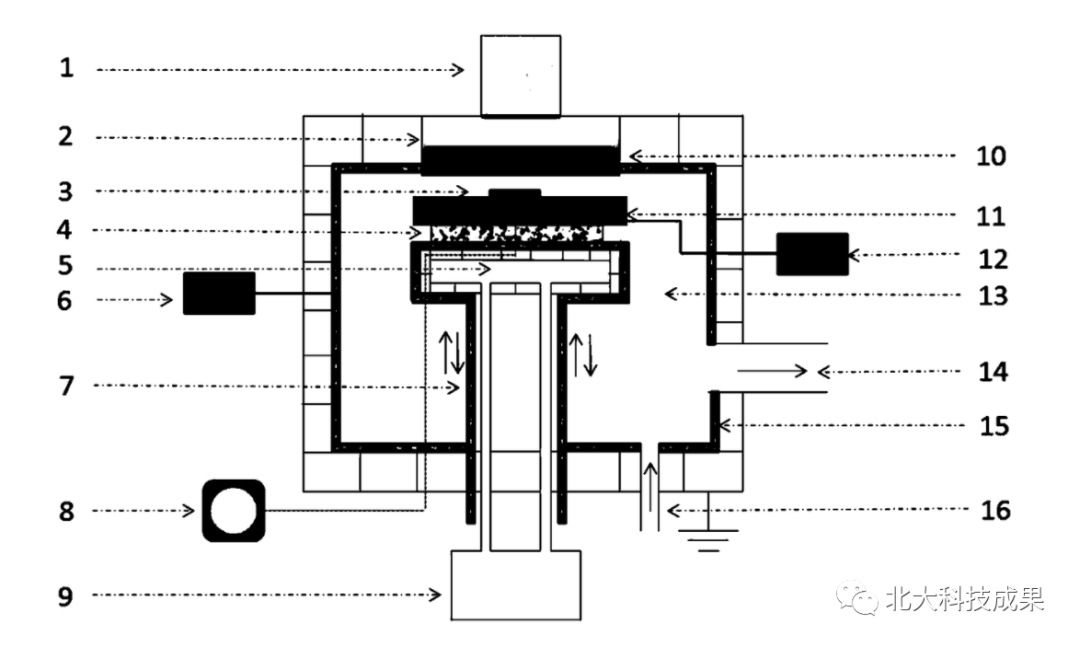

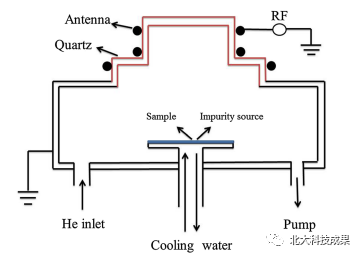

P1项目简介

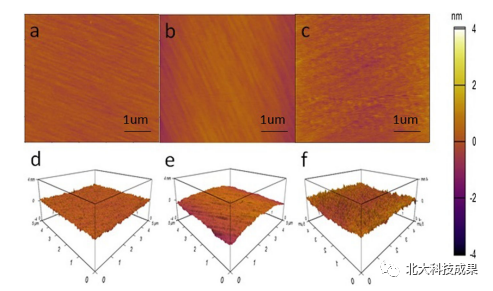

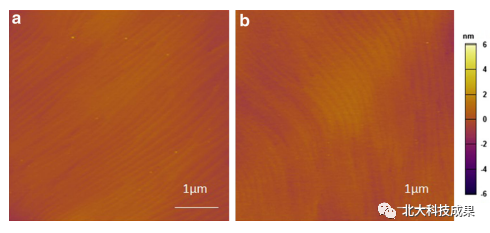

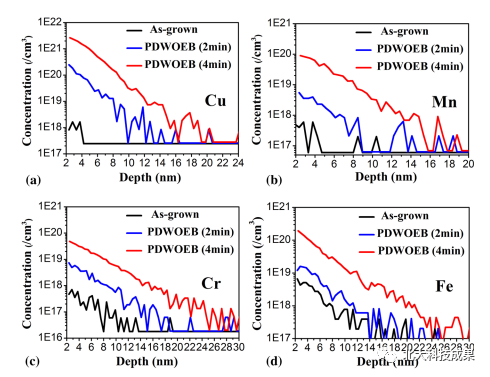

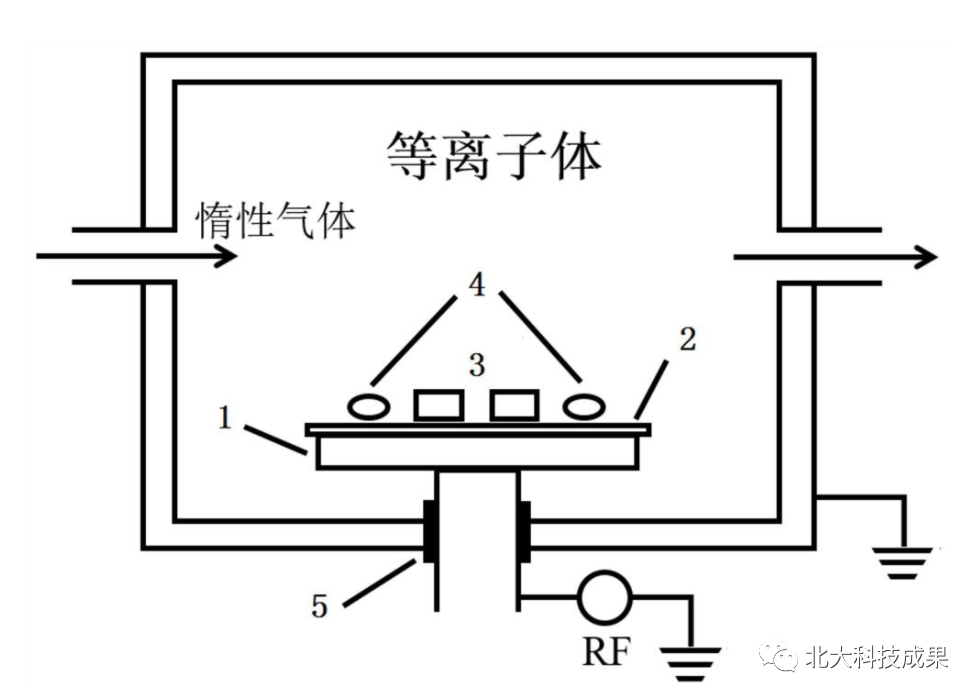

P2应用范围 可应用于多种半导体材料、半导体器件和芯片的半成品进行掺杂,如二极管、LED、太阳能电池、集成电路等半导体器件,特别可能适用于第三代半导体等新材料和新器件的掺杂。相较于离子注入和高温扩散等半导体常规掺杂方法,本项目方法是一种相对成本低廉、没有苛刻要求的新掺杂方法。 P3项目阶段 本项目目前处于实验室小试阶段。原来高温才能扩散的杂质,在等离子体作用下,室温或比室温稍高的温度下杂质就能扩散。如果延长时间,可使扩散距离增加。而增加温度,则扩散距离的增加更加明显。对Si,GaN, SiC,GaAs,AlN和氢化非晶Si的多种杂质进行的研究,证明此掺杂方法都适用。在我们的研究中,杂质离子浓度在半导体中的分布都是用二次离子质谱方法测定的(美国Evans公司、天津46研究所与中科院苏州纳米所测定)。 P4知识产权